# CS 261 Fall 2021

Mike Lam, Professor

| Stage | IRMOVQ                                   |

|-------|------------------------------------------|

| Fch   | $icode:ifun \leftarrow M_1[PC]$          |

|       | $rA:rB \leftarrow M_1[PC+1]$             |

|       | $valC \leftarrow M_8[PC+2]$              |

|       | $valP \leftarrow PC + 10$                |

| Dec   |                                          |

| Exe   | $\mathtt{valE} \leftarrow \mathtt{valC}$ |

| Mem   |                                          |

| WB -  | R[rB] ← valE                             |

| PC    | $PC \leftarrow valP$                     |

#### Y86 Semantics

#### Y86 semantics

- Semantics: the study of *meaning*

- What does an instruction "mean"?

- For us, it is the effect that it has on the machine

- This requires understanding the purpose and actions of all stages of the Y86-64 CPU

|            | Stage | IRMOVQ                                                       |

|------------|-------|--------------------------------------------------------------|

| Fetch      | Fch   | $\texttt{icode:ifun}  \leftarrow  \texttt{M}_1[\texttt{PC}]$ |

|            |       | $rA:rB \leftarrow M_1[PC+1]$                                 |

|            |       | $\texttt{valC} \leftarrow \texttt{M}_8 \texttt{[PC+2]}$      |

|            |       | valP ← PC + 10                                               |

| Decode     | Dec   |                                                              |

| Execute    | Exe   | $valE \leftarrow valC$                                       |

|            |       |                                                              |

| Memory     | Mem   |                                                              |

| Write back | WB    | $R[rB] \leftarrow valE$                                      |

|            | PC -  | PC ← valP                                                    |

| PC update  | 10    | 10 , , , , ,                                                 |

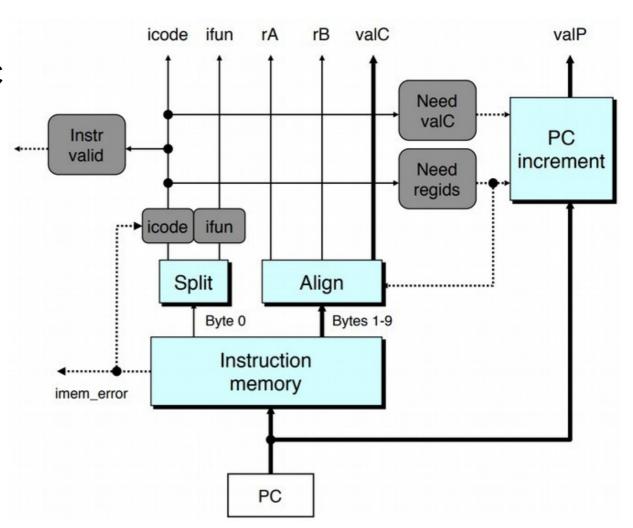

#### **Fetch**

- Read ten bytes from memory at address PC

- Extract instruction fields

- icode and ifun

- rA and rB

- valC

- Compute valP (address of next instruction)

- PC + 1 + needsRegIDs+ 8\*needsValC

Q: Which instructions have a valC? Which instructions only need the icode and ifun?

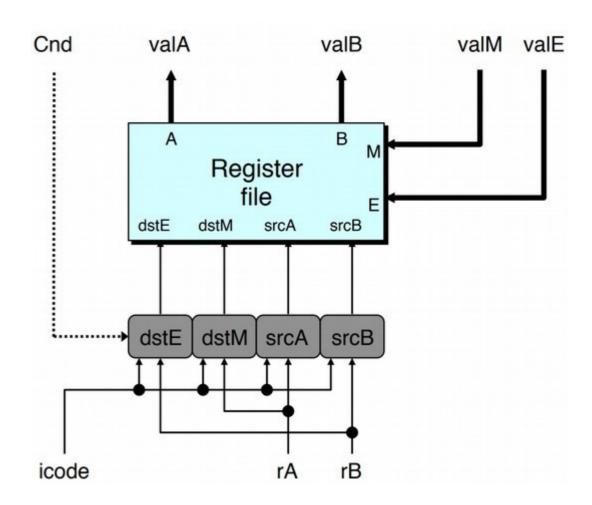

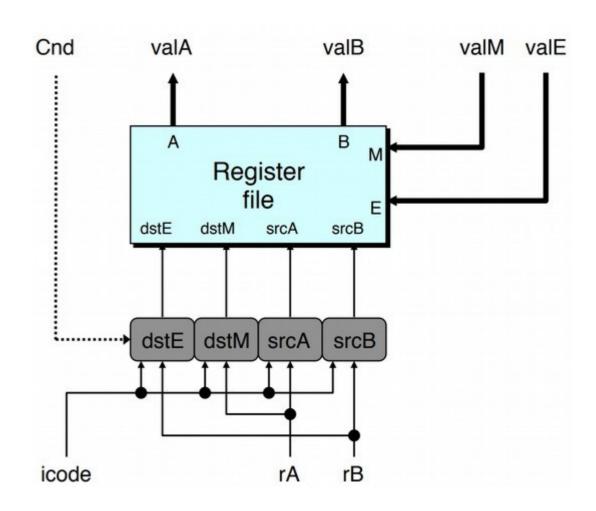

#### Decode

- Read register file

- Read srcA into valA

- Read srcB into valB

Q: Which instructions read from both rA and rB?

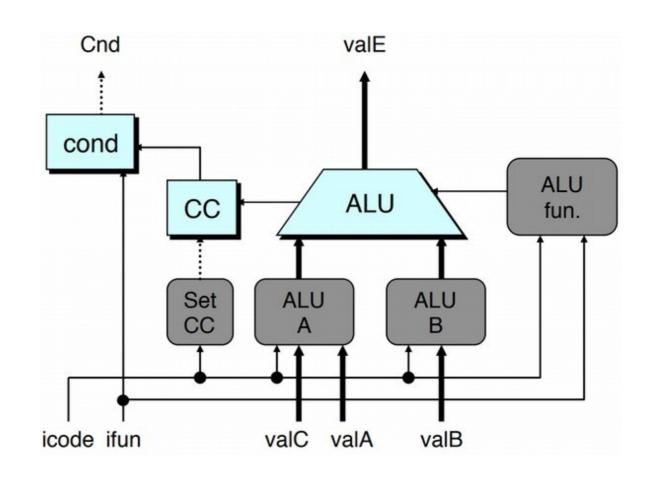

#### Execute

- Perform arithmetic or logic operation

- Could also be an effective address calculation or stack pointer increment / decrement

- First input is valC (immediate/offset), valA (register), or a constant (-8 or 8)

- Second input is valB (register) or zero

- Set condition codes

- Only if OPq

Q: Which instructions use the ALU? (Hint: more than you might initially expect!)

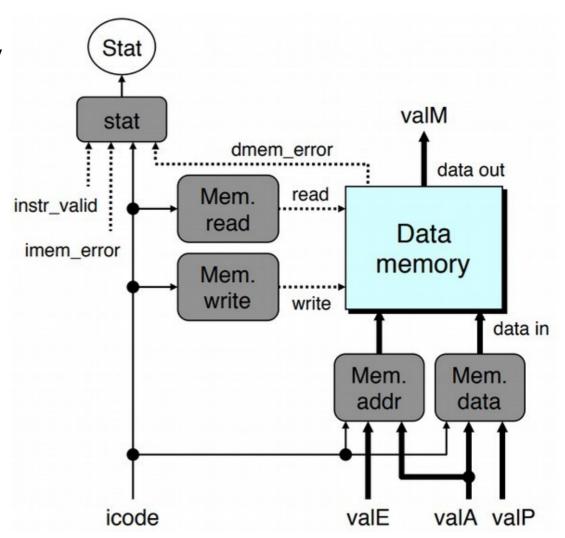

#### Memory

- Read or write memory

- No instruction does both!

- Effective address is valE or valA (depending on icode)

- Data to be written is either valA or valP (depending on icode)

- Data is read into valM

Q: Which instruction needs to write the address of the next instruction (valP) to memory?

#### Write back

- Write register file

- Write valE (from ALU execute) to dstE for some icodes

- Write valM (from memory) to dstM for some icodes

- Use value 0xF to disable one or both write(s) for some icodes

Q: Which instruction needs to write values to two different registers?

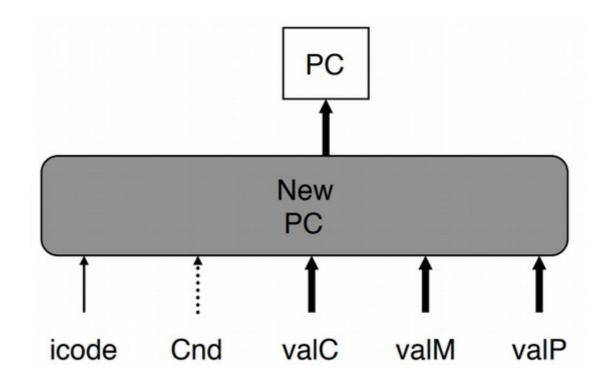

# PC update

#### Set new PC

- valP (next instruction) for most icodes

- Either valP or valC for conditional jumps depending on Cnd

- valM (return address popped from stack) for ret

## Question

What effect does the following instruction have?

irmovq \$128, %rsp

- A) It sets RSP to 128

- B) It moves the 64-bit value 128 into memory at the location stored in RSP

- C) It sets RSP to 128 and increments the PC by 10

- D) It pushes the value 128 onto the stack

- E) It pushes the value at address 128 onto the stack

#### Y86 semantics

- Semantics: the study of meaning

- For us, it is the effect that it has on the machine

- We should specify these semantics very formally

- This will help us think correctly about P4

- ISA reference sheet includes mathematical semantics

In the following semantics, PC and STAT refer to the program counter and status code of the CPU.

| Stage | HALT                                                       | NOP                                                        | cmovXX                                                              | IRMOVQ                                                     |

|-------|------------------------------------------------------------|------------------------------------------------------------|---------------------------------------------------------------------|------------------------------------------------------------|

| Fch   | $\texttt{icode:ifun} \leftarrow \texttt{M}_1[\texttt{PC}]$ | $\texttt{icode:ifun} \leftarrow \texttt{M}_1[\texttt{PC}]$ | $\texttt{icode:ifun} \leftarrow \texttt{M}_1[\texttt{PC}]$          | $\texttt{icode:ifun} \leftarrow \texttt{M}_1[\texttt{PC}]$ |

|       |                                                            |                                                            | $rA:rB \leftarrow M_1[PC+1]$                                        | $rA:rB \leftarrow M_1[PC+1]$                               |

|       |                                                            |                                                            |                                                                     | $\mathtt{valC} \leftarrow \mathtt{M}_8 \mathtt{[PC+2]}$    |

|       | valP ← PC + 1                                              | valP ← PC + 1                                              | $\mathtt{valP} \leftarrow \mathtt{PC} + \mathtt{2}$                 | valP ← PC + 10                                             |

| Dec   |                                                            |                                                            | $\texttt{valA} \leftarrow \texttt{R[rA]}$                           |                                                            |

| Exe   | STAT ← HLT                                                 |                                                            | $	exttt{valE} \leftarrow 	exttt{valA}$                              | $	exttt{valE} \leftarrow 	exttt{valC}$                     |

|       |                                                            |                                                            | $\texttt{Cnd} \leftarrow \texttt{Cond}(\texttt{CC}, \texttt{ifun})$ |                                                            |

| Mem   |                                                            |                                                            |                                                                     |                                                            |

| WB    |                                                            |                                                            | Cnd ? $R[rB] \leftarrow valE$                                       | $R[rB] \leftarrow valE$                                    |

| PC    | $PC \leftarrow valP$                                       | PC ← valP                                                  | PC ← valP                                                           | PC ← valP                                                  |

## Aside: syntax notes

- R[RSP] = the value of %rsp

- R[rA] = the value of register with id rA

- $M_1[PC]$  = the value of one byte in memory at address PC

- $M_8[PC+2]$  = the value of eight bytes in memory at address PC+2

- rA:rB =  $M_1[PC+1]$  means read the byte at address PC+1

- Split it into high- and low-order 4-bits for rA and rB

- Cond(CC, ifun) returns 0 or 1 based on CC and ifun

- Determines whether the given CMOV/JUMP should happen

- Convention: write addresses using hex padded to three chars

- Convention: write integer literals using decimal w/ no padding

## Example: IRMOVQ

irmovq \$128, %rsp

| Stage | IRMOVQ                          |  |  |  |

|-------|---------------------------------|--|--|--|

| Fch   | icode:ifun $\leftarrow M_1[PC]$ |  |  |  |

|       | $rA:rB \leftarrow M_1[PC+1]$    |  |  |  |

|       | $valC \leftarrow M_8[PC+2]$     |  |  |  |

|       | valP ← PC + 10                  |  |  |  |

| Dec   |                                 |  |  |  |

| Exe   | valE ← valC                     |  |  |  |

| Mem   |                                 |  |  |  |

| WB -  | R[rB] ← valE                    |  |  |  |

| PC    | PC ← valP                       |  |  |  |

```

icode:ifun \leftarrow M<sub>1</sub>[0x016] = 3:0

rA:rB \leftarrow M<sub>1</sub>[0x017] = f:4

valC \leftarrow M<sub>8</sub>[0x018] = 128

valP \leftarrow 0x016 + 10 = 0x020

```

What effects does this instruction have?

## Example: IRMOVQ

```

irmovq $128,%rsp

Stage

IRMOVQ

icode:ifun \leftarrow M<sub>1</sub>[PC]

Fch

icode:ifun \leftarrow M<sub>1</sub>[0x016] = 3:0

rA:rB \leftarrow M_1[PC+1]

rA:rB \leftarrow M_1[0x017] = f:4

valC \leftarrow M_8[0x018] = 128

valC \leftarrow M_8[PC+2]

valP \leftarrow 0x016 + 10 = 0x020

valP \leftarrow PC + 10

Dec

Exe

valE ← valC

valE ← 128

Mem

R[\%rsp] \leftarrow valE = 128

WB

R[rB] \leftarrow valE

PC \leftarrow valP = 0x020

PC

PC \leftarrow valP

```

This instruction sets %rsp to 128 and increments the PC by 10

# Example: POPQ

```

0x02c: b00f

%rax

popq

R[\%rsp] = 120

M_{8}[120] = 9

POPQ

Stage

icode:ifun \leftarrow M_1[0x02c] = b:0

icode:ifun \leftarrow M_1[PC]

Fch

rA:rB \leftarrow M_1[0x02d] = 0:f

rA:rB \leftarrow M_1[PC+1]

valP \leftarrow 0x02c + 2 = 0x02e

valP \leftarrow PC + 2

valA \leftarrow R[\%rsp] = 120

valA \leftarrow R[RSP]

Dec

valB \leftarrow R[%rsp] = 120

valB \leftarrow R[RSP]

valE \leftarrow 120 + 8 = 128

valE \leftarrow valB + 8

Exe

valM \leftarrow M_8[120] = 9

Mem

valM \leftarrow M_8[valA]

R[\%rsp] \leftarrow 128

WB

R[RSP] \leftarrow valE

R[\%rax] \leftarrow 9

R[rA] \leftarrow valM

PC

PC \leftarrow valP

PC \leftarrow 0x02e

```

This instruction sets %rax to 9, sets %rsp to 128, and increments the PC by 2

## Example: CALL

```

0x037: 804100000000000000

call proc

R[\%rsp] = 128

Stage

CALL

icode:ifun \leftarrow M<sub>1</sub>[0x037]=8:0

icode:ifun \leftarrow M_1[PC]

Fch

valC \leftarrow M_8[0x038] = 0x041

valC \leftarrow M<sub>8</sub>[PC+1]

valP \leftarrow 0x037 + 9 = 0x040

valP \leftarrow PC + 9

Dec

valB \leftarrow R[\%rsp] = 128

valB \leftarrow R[RSP]

valE \leftarrow 128 - 8 = 120

valE ← valB - 8

Exe

Mem

M_8[valE] \leftarrow valP

M_8[120] \leftarrow 0x040

WB

R[RSP] \leftarrow valE

R[\%rsp] \leftarrow 120

PC \leftarrow 0x041

PC

PC ← valC

```

This instruction sets %rsp to 120, stores the return address 0x040 at [%rsp], and sets the PC to 0x041

#### Y86 semantics

In the following semantics, PC and STAT refer to the program counter and status code of the CPU.

|       |                                                            | NOP                                                        | cmovXX                                                             |                                                            |

|-------|------------------------------------------------------------|------------------------------------------------------------|--------------------------------------------------------------------|------------------------------------------------------------|

| Stage | HALT                                                       | 1.91                                                       |                                                                    | IRMOVQ                                                     |

| Fch   | $\texttt{icode:ifun} \leftarrow \texttt{M}_1[\texttt{PC}]$ | $\texttt{icode:ifun} \leftarrow \texttt{M}_1[\texttt{PC}]$ | icode:ifun $\leftarrow M_1[PC]$                                    | icode:ifun $\leftarrow M_1[PC]$                            |

|       |                                                            |                                                            | $\texttt{rA:rB} \leftarrow \texttt{M}_1[\texttt{PC+1}]$            | $rA:rB \leftarrow M_1[PC+1]$                               |

|       | 1D / DG / 4                                                | 1D / DG / 1                                                | 1D / DG / O                                                        | valC ← M <sub>8</sub> [PC+2]                               |

| - =   | valP ← PC + 1                                              | valP ← PC + 1                                              | valP ← PC + 2                                                      | valP ← PC + 10                                             |

| Dec   | - <u></u>                                                  |                                                            | $valA \leftarrow R[rA]$                                            | <del> </del>                                               |

| Exe   | STAT ← HLT                                                 |                                                            | valE ← valA                                                        | $	ext{valE} \leftarrow 	ext{valC}$                         |

|       |                                                            |                                                            |                                                                    |                                                            |

| Mem   |                                                            |                                                            | <i></i>                                                            | <br>                                                       |

| WB    |                                                            |                                                            | $\texttt{Cnd ? R[rB]} \leftarrow \texttt{valE}$                    | R[rB] ← valE                                               |

| PC    | PC ← valP                                                  | PC ← valP                                                  | PC ← valP                                                          | PC ← valP                                                  |

| Stage | RMMOVQ                                                     | MRMOVQ                                                     | OPq                                                                | jXX                                                        |

| Fch   | $\texttt{icode:ifun} \leftarrow \texttt{M}_1[\texttt{PC}]$ | $icode:ifun \leftarrow M_1[PC]$                            | $\texttt{icode:ifun} \leftarrow \texttt{M}_1[\texttt{PC}]$         | icode:ifun $\leftarrow$ M <sub>1</sub> [PC]                |

|       | $rA:rB \leftarrow M_1[PC+1]$                               | $rA:rB \leftarrow M_1[PC+1]$                               | $rA:rB \leftarrow M_1[PC+1]$                                       |                                                            |

|       | $valC \leftarrow M_8[PC+2]$                                | $valC \leftarrow M_8[PC+2]$                                |                                                                    | $valC \leftarrow M_8[PC+1]$                                |

|       | valP ← PC + 10                                             | valP ← PC + 10                                             | $\mathtt{valP} \leftarrow \mathtt{PC} + 2$                         | valP ← PC + 9                                              |

| Dec   | $\mathtt{valA} \leftarrow \mathtt{R[rA]}$                  |                                                            | $\mathtt{valA} \leftarrow \mathtt{R[rA]}$                          |                                                            |

|       | $valB \leftarrow R[rB]$                                    | $\texttt{valB} \leftarrow \texttt{R[rB]}$                  | $\texttt{valB} \leftarrow \texttt{R[rB]}$                          |                                                            |

| Exe   | valE ← valB + valC                                         | $	ext{valE} \leftarrow 	ext{valB} + 	ext{valC}$            | $	exttt{valE} \leftarrow 	exttt{valB} \ 	exttt{OP} \ 	exttt{valA}$ | Cnd ← Cond(CC,ifun)                                        |

|       |                                                            |                                                            | Set CC                                                             |                                                            |

| Mem   | $M_8[valE] \leftarrow valA$                                | $valM \leftarrow M_8[valE]$                                |                                                                    | T                                                          |

| WB _  |                                                            | $R[rA] \leftarrow valM$                                    | $R[rB] \leftarrow valE$                                            | T                                                          |

| PC    | $\texttt{PC} \leftarrow \texttt{valP}$                     | PC ← valP                                                  | PC ← valP                                                          | $PC \leftarrow Cnd ? valC:valP$                            |

| Stage | CALL                                                       | RET                                                        | PUSHQ                                                              | POPQ                                                       |

| Fch   | icode:ifun $\leftarrow$ M <sub>1</sub> [PC]                | $\texttt{icode:ifun} \leftarrow \texttt{M}_1[\texttt{PC}]$ | $\texttt{icode:ifun} \leftarrow \texttt{M}_1[\texttt{PC}]$         | $\texttt{icode:ifun} \leftarrow \texttt{M}_1[\texttt{PC}]$ |

|       |                                                            |                                                            | $rA:rB \leftarrow M_1[PC+1]$                                       | $rA:rB \leftarrow M_1[PC+1]$                               |

|       | $\texttt{valC} \leftarrow \texttt{M}_8 \texttt{[PC+1]}$    |                                                            |                                                                    |                                                            |

|       | valP ← PC + 9                                              | valP ← PC + 1                                              | $\mathtt{valP} \leftarrow \mathtt{PC} + \mathtt{2}$                | valP ← PC + 2                                              |

| Dec   |                                                            | $\texttt{valA} \leftarrow \texttt{R[RSP]}$                 | $valA \leftarrow R[rA]$                                            | valA ← R[RSP]                                              |

|       | $\texttt{valB} \leftarrow \texttt{R[RSP]}$                 | $\texttt{valB} \leftarrow \texttt{R[RSP]}$                 | $\texttt{valB} \leftarrow \texttt{R[RSP]}$                         | $\texttt{valB} \leftarrow \texttt{R[RSP]}$                 |

| Exe   | valE ← valB - 8                                            | valE ← valB + 8                                            | valE ← valB - 8                                                    | valE ← valB + 8                                            |

| Mem   | $M_8[valE] \leftarrow valP$                                | $valM \leftarrow M_8[valA]$                                | $M_8[valE] \leftarrow valA$                                        | $valM \leftarrow M_8[valA]$                                |

| WB    | $R[RSP] \leftarrow valE$                                   | $R[RSP] \leftarrow valE$                                   | $R[RSP] \leftarrow valE$                                           | $R[RSP] \leftarrow valE$                                   |

|       |                                                            |                                                            |                                                                    | $R[rA] \leftarrow valM$                                    |

| PC -  | PC ← valC                                                  | PC ← valM                                                  | PC ← valP                                                          | PC ← valP                                                  |

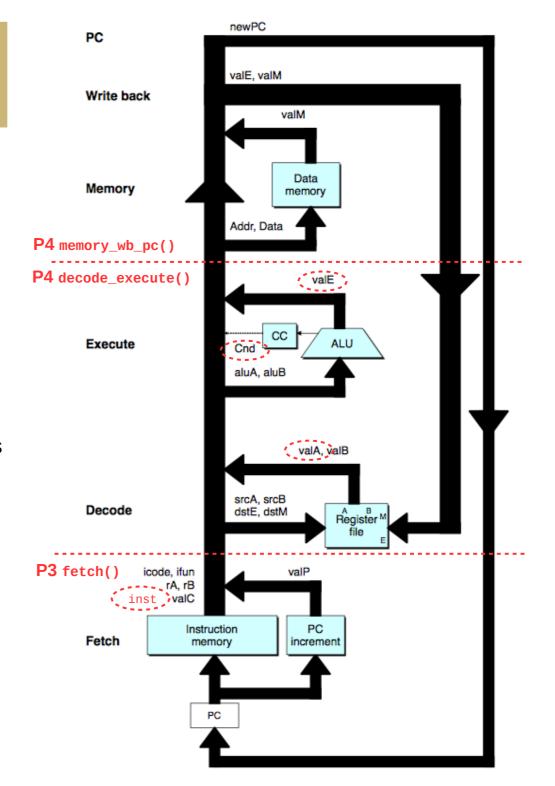

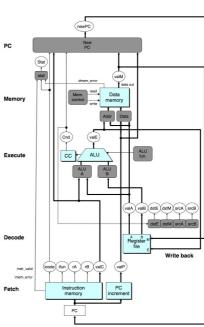

## Y86 CPU (P4)

#### von Neumann architecture

- 1) Fetch ← P3!

- Splits instruction at PC into pieces

- Save info in y86\_inst\_t struct

- 2) Decode (register file)

- Reads registers

- P4: Sets valA

- 3) Execute (ALU)

- Arithmetic/logic operation, effective address calculation, or stack pointer increment/decrement

- P4: Sets cnd and returns vale

- 4) Memory (RAM)

- Reads/writes memory

- 5) Write back (register file)

- Sets registers

- 6) PC update

- Sets new PC